dsp系统时钟,dsp时钟

时间:2024-11-04 来源:网络 人气:

数字信号处理器(DSP)作为数字信号处理的核心设备,广泛应用于通信、音频、视频、工业控制等领域。DSP系统的性能很大程度上取决于其时钟系统的设计。本文将详细介绍DSP系统时钟的基本概念、设计原则以及在实际应用中的注意事项。

一、DSP系统时钟的基本概念

1. 时钟频率

时钟频率是DSP系统时钟的基本参数,它决定了DSP处理数据的速度。时钟频率越高,DSP的处理速度越快,但同时也增加了功耗和发热量。

2. 时钟源

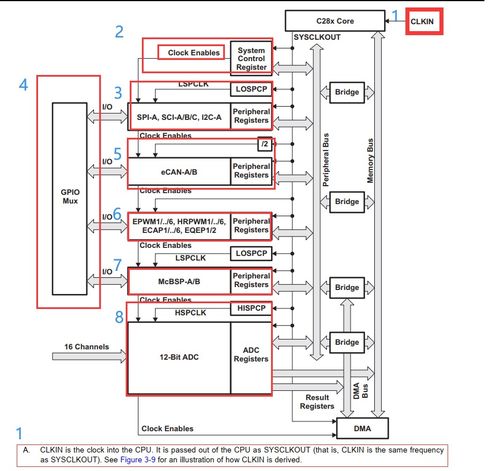

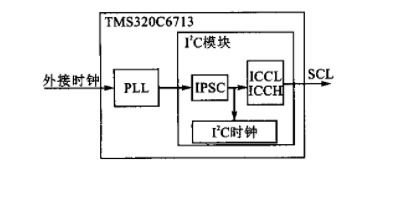

时钟源是提供时钟信号的设备,常见的时钟源有晶振、陶瓷谐振器、PLL(锁相环)等。晶振具有稳定性好、成本低等优点,但频率范围有限;陶瓷谐振器频率范围较宽,但稳定性略逊于晶振;PLL可以将低频时钟信号倍频,提高系统时钟频率。

3. 时钟分频

时钟分频是将高频率的时钟信号转换为低频率的时钟信号,以满足不同模块对时钟频率的需求。常见的时钟分频方式有固定分频、可编程分频等。

二、DSP系统时钟设计原则

1. 稳定性

时钟信号是DSP系统正常运行的基础,因此时钟信号必须稳定可靠。在设计时钟系统时,应选择高稳定性的时钟源,并采取必要的抗干扰措施。

2. 可靠性

时钟系统应具有较高的可靠性,以防止因时钟故障导致系统崩溃。在设计时钟系统时,应考虑冗余设计,如双时钟源、双时钟分频器等。

3. 可扩展性

随着系统功能的扩展,时钟系统的设计应具有一定的可扩展性,以满足未来系统升级的需求。

4. 功耗优化

时钟系统设计应考虑功耗优化,以降低系统功耗,提高能效。

三、DSP系统时钟在实际应用中的注意事项

1. 时钟域交叉

在多时钟域设计中,时钟域交叉问题可能导致系统性能下降或故障。在设计时钟系统时,应采取必要的隔离措施,如时钟域同步、时钟域转换等。

2. 时钟抖动

时钟抖动是指时钟信号在时间上的波动,过大的时钟抖动会影响DSP系统的性能。在设计时钟系统时,应选择低抖动的时钟源,并采取滤波、去抖等措施。

3. 时钟偏移

时钟偏移是指不同模块之间时钟信号的相位差,过大的时钟偏移可能导致系统性能下降。在设计时钟系统时,应尽量减小时钟偏移,如采用同步时钟源、同步时钟分频等。

4. 时钟域划分

在复杂系统中,时钟域划分是提高系统性能的关键。合理划分时钟域,可以降低系统功耗,提高系统稳定性。

DSP系统时钟是影响系统性能的关键因素,设计合理的时钟系统对于提高系统性能、降低功耗具有重要意义。本文从基本概念、设计原则和实际应用等方面对DSP系统时钟进行了详细介绍,希望对读者有所帮助。

相关推荐

教程资讯

教程资讯排行