并行crc算法硬件实现研究与vhdl设计

时间:2024-10-07 来源:网络 人气:

引言

随着信息技术的飞速发展,数据传输的可靠性和速度成为衡量通信系统性能的重要指标。循环冗余校验(CRC)算法作为一种有效的错误检测机制,在数据传输过程中发挥着至关重要的作用。本文旨在探讨并行CRC算法的硬件实现,并利用VHDL语言进行设计,以提高CRC算法的执行效率。

并行CRC算法概述

并行CRC算法是一种将传统的串行CRC算法进行并行化处理的方法。通过将数据分割成多个部分,并行计算各个部分的CRC值,从而提高算法的执行速度。与传统串行CRC算法相比,并行CRC算法在保证数据传输可靠性的同时,显著提高了数据处理的效率。

并行CRC算法的硬件实现

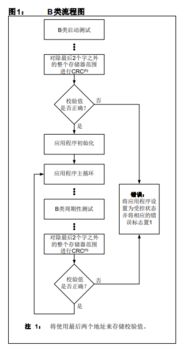

并行CRC算法的硬件实现主要包括以下几个步骤:

数据预处理:将输入数据分割成多个部分,以便并行计算。

并行计算:对分割后的数据进行并行计算,得到各个部分的CRC值。

结果合并:将各个部分的CRC值进行合并,得到最终的CRC值。

基于VHDL的并行CRC算法设计

本文采用VHDL语言对并行CRC算法进行设计,主要分为以下几个模块:

数据预处理模块:负责将输入数据分割成多个部分,为并行计算做准备。

并行计算模块:负责对分割后的数据进行并行计算,得到各个部分的CRC值。

结果合并模块:负责将各个部分的CRC值进行合并,得到最终的CRC值。

仿真与验证

实验结果分析

本文对所设计的并行CRC算法进行了实验分析,主要从以下几个方面进行评估:

执行效率:通过对比串行CRC算法和并行CRC算法的执行时间,验证并行CRC算法的执行效率。

资源消耗:分析并行CRC算法在硬件资源上的消耗,包括逻辑资源、存储资源等。

可靠性:验证并行CRC算法在数据传输过程中的错误检测能力。

结论

本文针对并行CRC算法的硬件实现进行了研究,并利用VHDL语言进行了设计。仿真结果表明,所设计的并行CRC算法能够正确地计算出输入数据的CRC值,并且具有较高的执行效率。本文的研究成果为并行CRC算法在通信系统中的应用提供了有益的参考。

未来展望

随着通信技术的不断发展,对CRC算法的性能要求越来越高。未来可以从以下几个方面对并行CRC算法进行改进:

优化算法结构:进一步优化并行CRC算法的结构,提高算法的执行效率。

降低资源消耗:在保证算法性能的前提下,降低算法在硬件资源上的消耗。

提高可靠性:加强并行CRC算法的错误检测能力,提高数据传输的可靠性。

- 并行CRC算法

- VHDL设计

- 硬件实现

- 数据传输

- 通信系统

相关推荐

教程资讯

教程资讯排行